## Gate-Level Minimization

#### Jee-Hwan Ryu

#### School of Mechanical Engineering Korea University of Technology and Education

#### Gate-Level Minimization-The Map Method

- Truth table is unique

- Many different algebraic expression

- Boolean expressions may be simplified by algebraic means

- But, awkward due to the lack of specific rules

- Karnaugh Map or K-map method

- Pictorial form of truth table

- A simple and straight forward procedure

Korea University of Technology and Education

3/29

101

minimum number of inputs to the gate Simplest expression is not unique

Produces a circuit diagram with a

minimum number of gates and the

# Why Need to be Simple ?

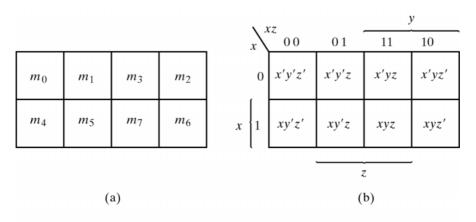

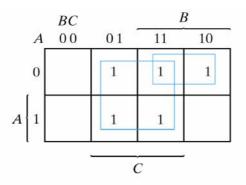

## Three-Variable Map

Not in a binary sequence, but in a sequence similar to Gray code

$$m_{5} + m_{7} = xy'z + xyz = xz(y + y') = xz$$

$$m_{0} + m_{2} = x'y'z' + x'yz' = x'z'(y' + y) = x'z'$$

Korea University of Technology and Education

Examples

Ex 3-1) Simplify the Boolean function,  $F(x, y, z) = \Sigma(2, 3, 4, 5)$

$$F = x'y + xy'$$

| x | <i>yz</i><br>0 0 | 01 | 11 | 10 |

|---|------------------|----|----|----|

| 0 |                  |    | 1  | 1  |

| 1 | 1                | 1  |    |    |

Fig. 3-4 Map for Example 3-1;  $F(x, y, z) = \Sigma(2, 3, 4, 5) = x'y + xy'$

Ex 3-4) Simplify the Boolean Function,  $F(x, y, z) = \Sigma(0, 2, 4, 5, 6)$

Korea University of Technology and Education

1 🗖 0 1

5/29

**d** 0 1

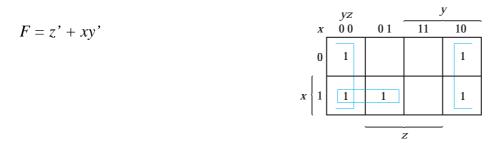

Ex 3-4) Given Boolean function, F = A'C + A'B + AB'C + BCa) express it in sum of minterms

$F(x, y, z) = \Sigma(1, 2, 3, 5, 7)$

b) find the minimal sum of products F = C + A'B

Fig. 3-7 Map for Example 3-4; A'C + A'B + AB'C + BC = C + A'B

Korea University of Technology and Education

7/29

**n –** n 1

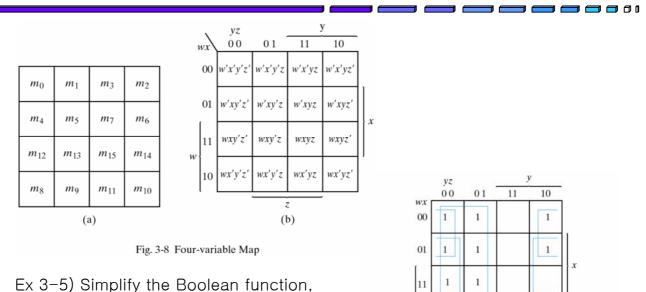

#### Four-Variable Map

$F(w, x, y, z) = \Sigma(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

$$F = y' + w'z' + xz$$

Fig. 3-9 Map for Example 3-5; F(w, x, y, z)=  $\Sigma$  (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14) = y' + w'z' + xz'

1

w

10

1

Korea University of Technology and Education

## Examples

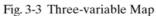

1. Simplify the Boolean function

$$F(x, y, z) = \Sigma(3, 4, 6, 7)$$

$$yz + xz'$$

2. Simplify the Boolean function

$F(x, y, z) = \Sigma(0, 2, 4, 5, 6)$

$$z' + xy'$$

Korea University of Technology and Education

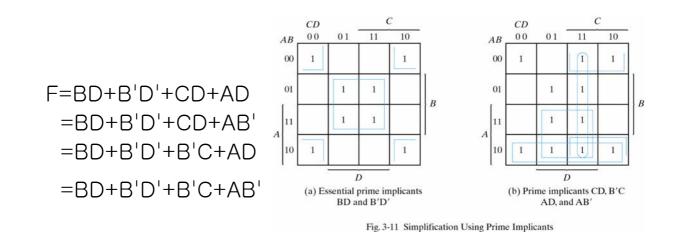

Prime Implicants

Prime Implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map.

$F(A,B,C,D) = \Sigma(0,2,3,5,7,8,9,10,11,13,15)$

Korea University of Technology and Education

**n –** a 1

9/29

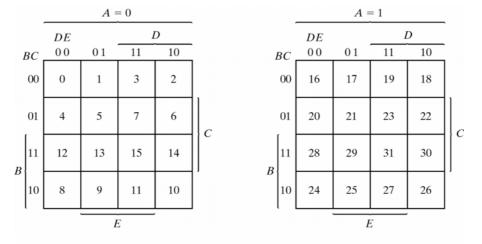

Fig. 3-12 Five-variable Map

11/29

**a a**

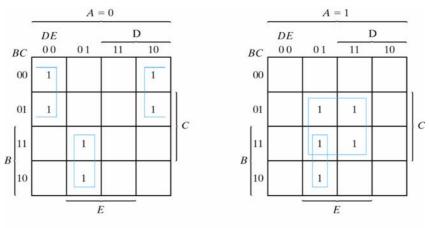

#### Example

Ex 3–7) Simplify the Boolean function,  $F(A,B,C,D,E) = \Sigma(0,2,4,6,9,13,21,23,25,29,31)$

Fig. 3-13 Map for Example 3-7; F = A'B'E' + BD'E + ACE

F = A'B'E' + BD'E + ACE

#### Examples

1. Simplify the following Boolean functions by first finding the essential prime implicants:

$F(A,B,C,D) = \Sigma(0,2,3,5,7,8,10,11,14,15)$

- i) find the essential prime implicants CD+B'D'

- ii) find the non essential prime implicants AC+A'BD

- iii) simplify function F CD+B'D'+AC+A'BD

- 2. Simplify the following Boolean functions, using five-variable maps:

F(A,B,C,D,E)=∑(0,1,4,5,16,17,21,25,29) Ans) A'B'D'+B'C'D'+AD'E

Korea University of Technology and Education

13/29

Korea University of Technology and Education

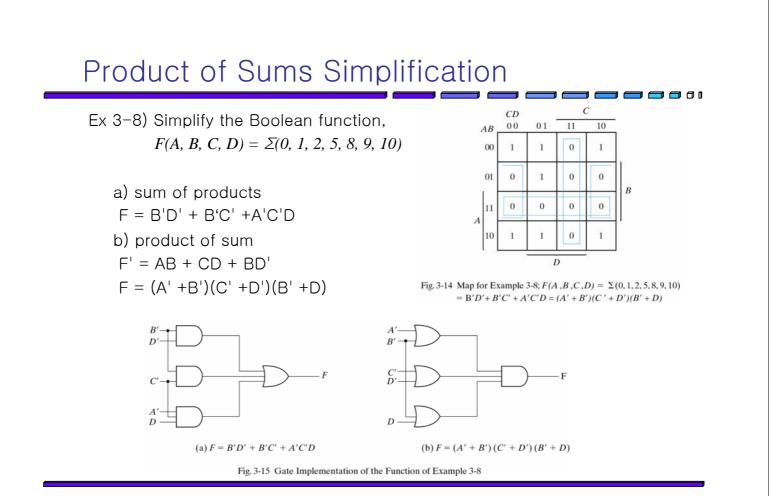

## Product of Sums Simplification

| Table | 3-2   |    |          |   |

|-------|-------|----|----------|---|

| Truth | Table | of | Function | F |

|       |       |    |          |   |

|   |   | the second se |   |

|---|---|-----------------------------------------------------------------------------------------------------------------|---|

| x | y | z                                                                                                               | F |

| 0 | 0 | 0                                                                                                               | 0 |

| 0 | 0 | 1                                                                                                               | 1 |

| 0 | 1 | 0                                                                                                               | 0 |

| 0 | 1 | 1                                                                                                               | 1 |

| 1 | 0 | 0                                                                                                               | 1 |

| 1 | 0 | 1                                                                                                               | 0 |

| 1 | 1 | 0                                                                                                               | 1 |

| 1 | 1 | 1                                                                                                               | 0 |

| уz |   |                  | у  |    |    |

|----|---|------------------|----|----|----|

|    | x | <i>yz</i><br>0 0 | 01 | 11 | 10 |

|    | 0 | 0                | 1  | 1  | 0  |

| x  | 1 | 1                | 0  | 0  | 1  |

|    |   |                  |    |    | ,  |

Fig. 3-16 Map for the Function of Table 3-2

$F(x, y, z) = \Sigma(1, 3, 4, 6) = \Pi(0, 2, 5, 7)$  F = x'z + xz' F' = xz + x'z'F = (x'+z')(x + z)

Korea University of Technology and Education

Examples

Simplify the following Boolean functions in product of sums:

1.  $F(w, x, y, z) = \Sigma(0, 2, 5, 6, 7, 8, 10)$ Ans) (w'+x')(x+z')(x'+y+z)

2.  $F(A,B,C,D) = \square(1,3,5,7,13,15)$ Ans) (B'+D')(A+D') 15/29

00

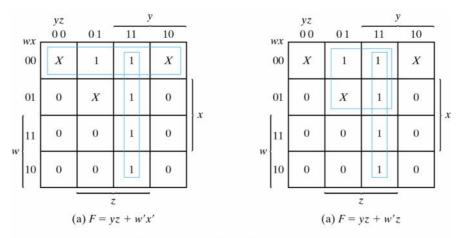

## Don't-Care Conditions

Ex 3-9) Simplify the Boolean function,  $F(w, x, y, z) = \Sigma(1,3,7,11,15)$ Don't-care conditions,  $d(w, x, y, z) = \Sigma(0, 2, 5)$

Fig. 3-17 Example with don't-care Conditions

$F(w, x, y, z) = yz + w'x' = \Sigma(0, 1, 2, 3, 7, 11, 15)$  $F(w, x, y, z) = yz + w'z = \Sigma(1, 3, 5, 7, 11, 15)$

Korea University of Technology and Education

17/29

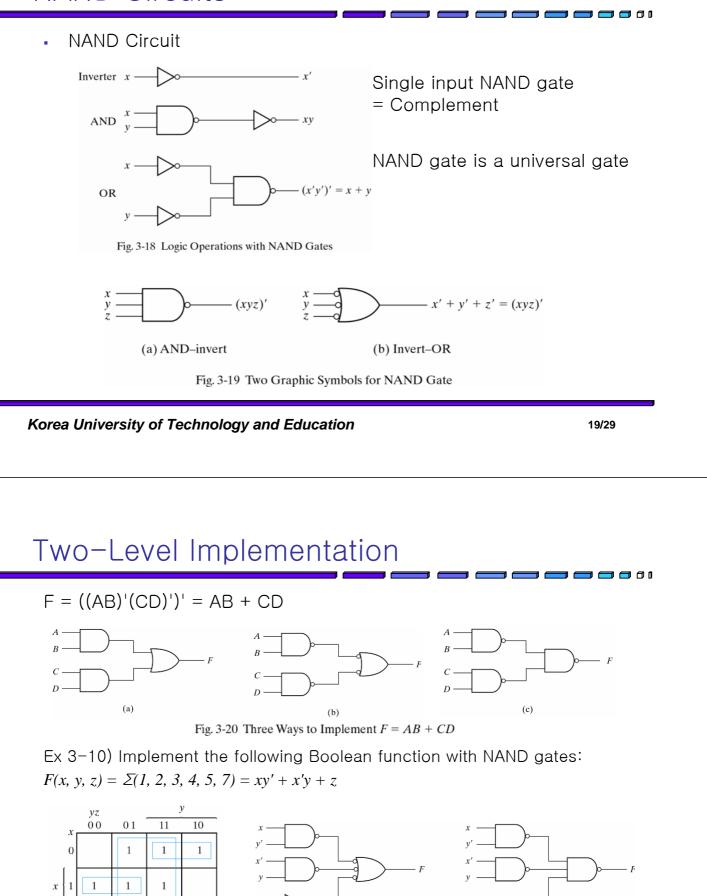

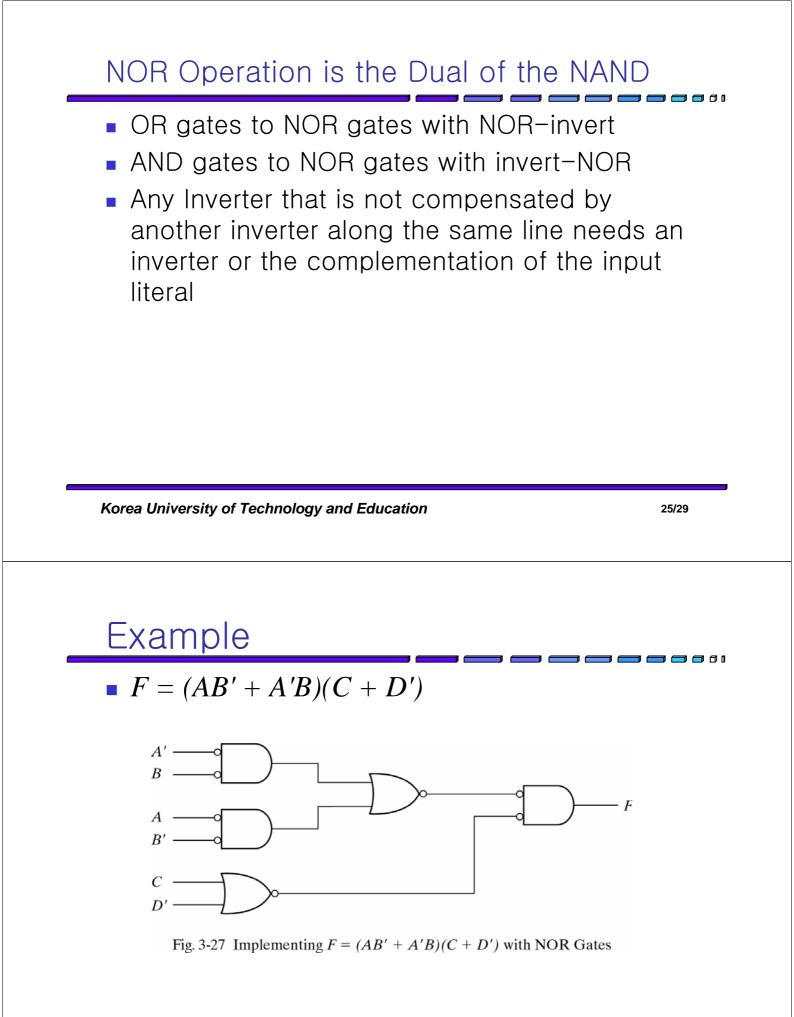

### NAND and NOR Implementation

- Digital circuits are frequently constructed with NAND or NOR gates rather than AND and OR gates

- NAND and NOR gates are easier to fabricate with electronic components

- Basic gates used in all IC digital logic families

## NAND Circuits

Fig. 3-21 Solution to Example 3-10

(b)

Korea University of Technology and Education

z

(c)

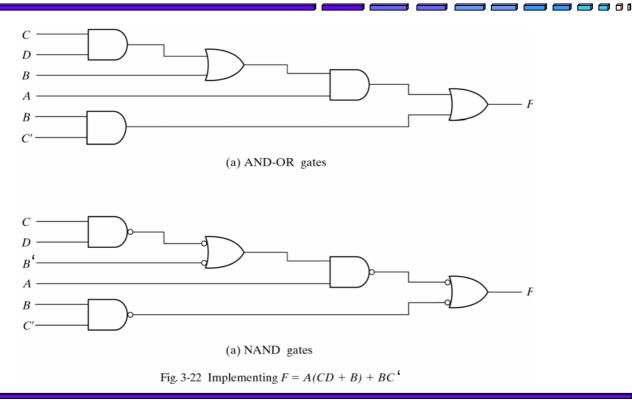

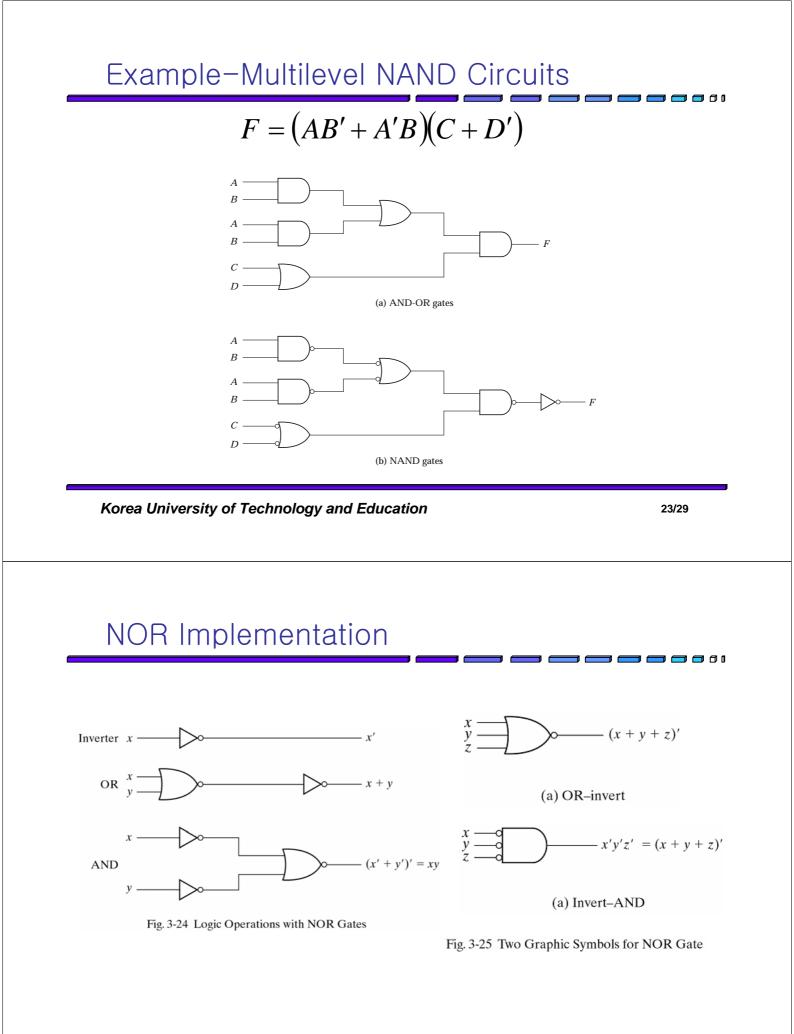

## Multilevel NAND Circuits

- Convert all AND to NAND with NAND-inverter

- Convert all OR to NAND with inverter-NAND

- Check all the inverter in the diagram. For every inverter that is not compensated by another circle along the same line, insert an inverter (one-input NAND gate) or complement the input literal

Korea University of Technology and Education

Example-Multilevel NAND Circuits

Korea University of Technology and Education

21/29

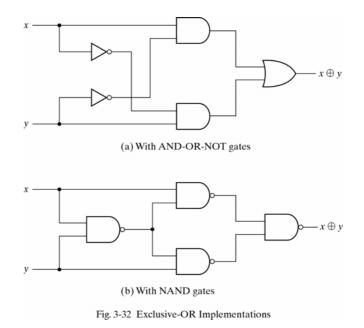

## Exclusive-OR Function

$XOR: x \oplus y = xy' + x'y$  $XNOR: (x \oplus y)' = xy + x'y'$

$x \oplus 0 = x$

$$x \oplus 1 = x'$$

$x \oplus x = 0$

$$x \oplus x' = 1$$

$$x \oplus y' = x' \oplus y = (x \oplus y)$$

Korea University of Technology and Education

27/29

] [] []

1 🗖 0 1

### Parity Generation and Checking

| ole 3<br>n-Par |             | rator Truth | Table                 |                      |    | Bits   |   | Parity Error<br>Check           |

|----------------|-------------|-------------|-----------------------|----------------------|----|--------|---|---------------------------------|

|                |             | 10          |                       | x                    | у  | z      | Р | c                               |

| hree           | -Bit Me     | ssage       | Parity Bit            | 0                    | 0  | 0      | 0 | 0                               |

| ~              |             | 7           | P                     | 0                    | 0  | 0      | 1 | 1                               |

| x              | У           | Z           | P                     | 0                    | 0  | 1      | 0 | 1                               |

| 0              | 0           | 0           | 0                     | 0                    | 0  | 1      | 1 | 0                               |

| 0              | -12         | 0           | 0                     | 0                    | 1  | 0      | 0 | 1                               |

| 0              | 0           | 1           | 1                     | 0                    | 1  | 0      | 1 | 0                               |

| 0              | 1           | 0           | 1                     | 0                    | 1  | 1      | 0 | 0                               |

| 0              | 1           | 1           | 0                     | 0                    | 0  | 0      | 0 | 1                               |

| 1              | 0           | 0           | 1                     | 1                    | 0  | 0      | 1 | 0                               |

| 1              | 0           | 1           | 0                     | 1                    | 0  | 1      | 0 | 0                               |

| <u>.</u>       |             | 1           | 0                     | 1                    | 0  | i      | 1 | 1                               |

| 1              | 1           | 0           | 0                     | 1                    | 1  | 0      | 0 | 0                               |

| 1              | 1           | 1           | 1                     | 1                    | 1  | 0      | 1 | 1                               |

|                |             |             |                       | 1                    | 1  | 1      | 0 | 1                               |

|                |             |             |                       | 1                    | 1  | 1      | 1 | 0                               |

| <i>x</i> —     | -11         |             |                       | <i>x</i> –           | -1 |        |   |                                 |

| y —            | $\parallel$ |             | P                     | у —                  | /  |        |   | 1                               |

|                |             |             | Same circuit for che  | cking <sub>z –</sub> |    | _      |   | $+\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| z —            |             |             | and generation<br>P=0 | P -                  | ][ | $\sum$ |   |                                 |

Fig. 3-36 Logic Diagram of a Parity Generator and Checker

Korea University of Technology and Education

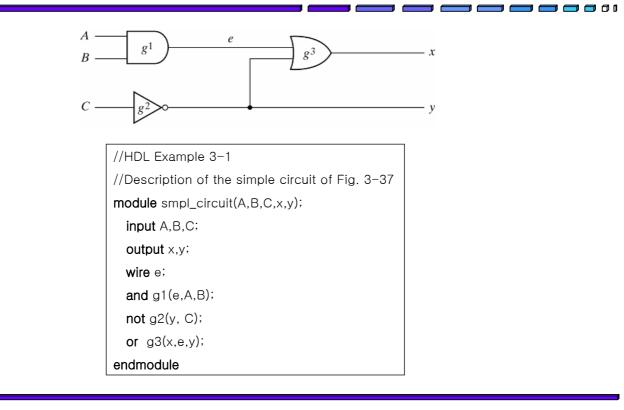

## HDL(Hardware Description Language)

Korea University of Technology and Education

29/29