MEC520 디지털 공학

# **Registers and Counters**

#### Jee-Hwan Ryu

School of Mechanical Engineering Korea University of Technology and Education

#### **Registers and Counters**

- Circuits that include flip-flops are usually classified by the function they perform

- Registers

- Counters

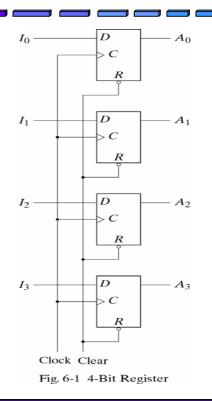

- Register is a group of flip-flops.

- Each flip-flop is capable of storing one bit of information.

- An n-bit register consists of a group of n flip-flops.

- Register is a group of binary cells suitable for holding binary information.

- A counter is essentially a register that goes through a predetermined sequence of states.

# Registers

- Clock= 0 to 1 ; Input information is transferred to output : I -> A

- Clock = 0 and 1; Output unchanged

- Clear = 0 ; Clearing the register to all 0's prior to its clocked operation.

- Clear : asynchronous input.

Korea University of Technology and Education

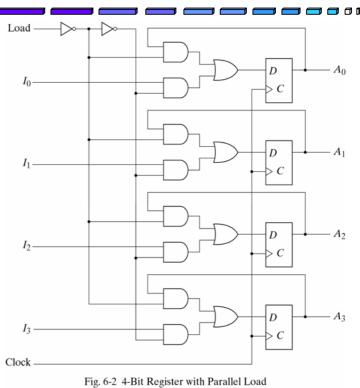

## Register with Parallel Load

- Synchronous digital systems have a master clock generator that supplies a continuous train of clock pulses.

- The transfer of new information into a register is referred to as loading the register.

- If all the bits of the register are loaded simultaneously with a common clock pulse, we say that the loading is done in parallel.

- The load input determines whether the next pulse will accept new information or leave the information in the register intact

#### Register with Parallel Load

- Load = 1 ; the | inputs are transferred into the register

- Load = 0 ; maintain the content of the register

- Because the D flip-flop does not have a "no change"

1 🗖 0 1

Korea University of Technology and Education

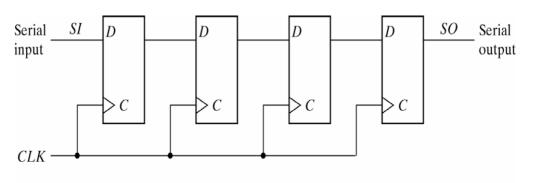

#### Shift Registers

Capable of shifting its binary information in one or both directions

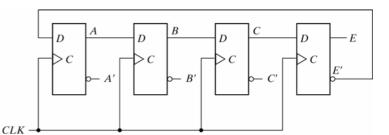

Fig. 6-3 4-Bit Shift Register

The simplest shift register

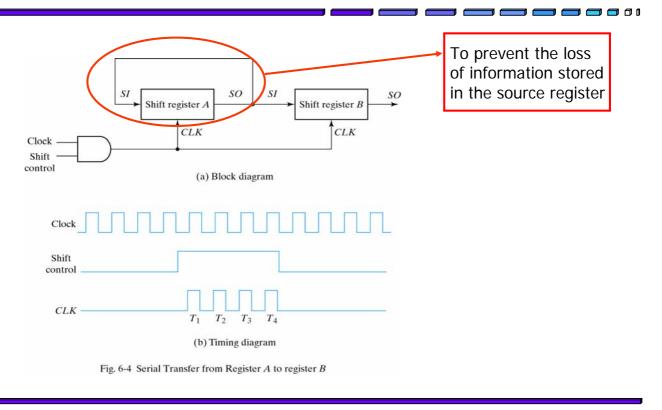

#### Shift Registers: Serial Transfer

Korea University of Technology and Education

#### Serial-Transfer Example

#### Table 6–1: Serial-Transfer Example

] (] (

| Timing pulse         | Shift register A | Shift register B | Serial output of B |

|----------------------|------------------|------------------|--------------------|

| Initial value        | 1011             | 0010             |                    |

| After T <sub>1</sub> | 1101             | 1001             | 0                  |

| After T <sub>2</sub> | 1110             | 1100             | 1                  |

| After T₃             | 0111             | 0110             | 0                  |

| After T₄             | 1011             | 1011             | 0                  |

|                      |                  |                  |                    |

A is transferred into B, while the content of A remains unchanged

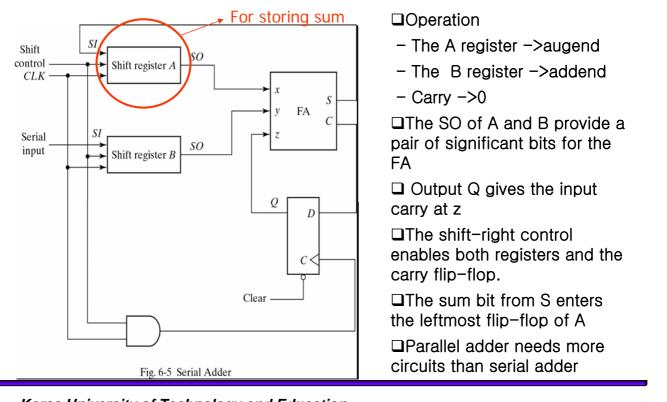

## Serial Addition

**n –** n 1

**d** 0 0

Korea University of Technology and Education

#### State Table for Serial Adder

| Present<br>State | Inp | uts | Next<br>State | Output | Flip-Flop<br>Inputs |   |  |

|------------------|-----|-----|---------------|--------|---------------------|---|--|

| Q                | X   | у   | Q             | S      | Jq                  | K |  |

| 0                | 0   | 0   | 0             | 0      | 0                   | Х |  |

| 0                | 0   | 1   | 0             | 1      | 0                   | Х |  |

| 0                | 1   | 0   | 0             | 1      | 0                   | Х |  |

| 0                | 1   | 1   | 1             | 0      | 1                   | Х |  |

| 1                | 0   | 0   | 0             | 1      | X                   | 1 |  |

| 1                | 0   | 1   | 1             | 0      | Х                   | 0 |  |

| 1                | 1   | 0   | 1             | 0      | X                   | 0 |  |

| 1                | 1   | 1   | 1             | 1      | Х                   | 0 |  |

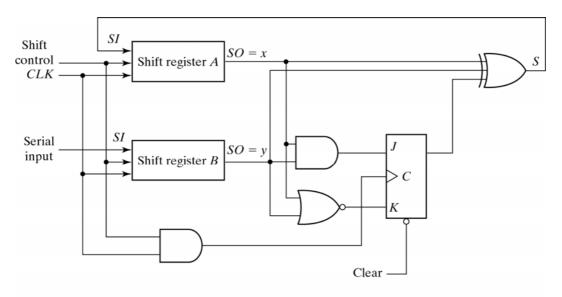

#### Second form of Serial Adder

101

Fig. 6-6 Second form of Serial Adder

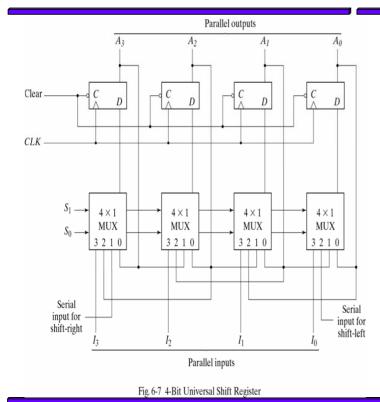

#### Universal Shift Register

- If the register has both shifts and parallel load capabilities, it is referred to as a universal shift register.

- A clear control to clear the register to 0.

- A clock input to synchronize the operations.

- A shift-right control to enable the shift right operation and the serial input and output lines associated with the shift right.

- A shift-left control to enable the shift left operation and the serial input and output lines associated with the shift left.

- A parallel-load control to enable a parallel transfer and the n input lines associated with the parallel transfer.

- n parallel output lines

- A control state that leaves the information in the register unchanged in the presence of the clock.

#### Universal Shift Register

$\Box S_1, S_0 \rightarrow 0, 0$ ; No change

$\Box$ S<sub>1</sub>, S<sub>0</sub> -> 0, 1 ; Shift right, The serial input for shift-right is transferred to the A3.

**n –** n n

$\Box S_1, S_0 \rightarrow 1, 0$ ; Shift left, The serial input for shift–left is transferred to the A0.

$\Box S_1$ ,  $S_0 \rightarrow 1$ , 1 ;Parallel load

# Korea University of Technology and Education

#### Universal Shift Register

- Shift register are often used to interface digital systems.

- Suppose it is necessary to transmit an n-bit quantity between two points.

- It will be expensive to use n lines to transmit the n bits in parallel.

- It is more economical to use a single line and transmit the information serially, one bit at a time.

- The transmitter accepts the n-bit data in parallel into a shift register and then transmits the data serially along the common line.

- The receiver accepts the data serially into a shift register.

- When all n-bits are received, they can be taken from the outputs of the register in parallel.

- The transmitter: a parallel-to-serial conversion of data, the receiver: a serial-to-parallel conversion.

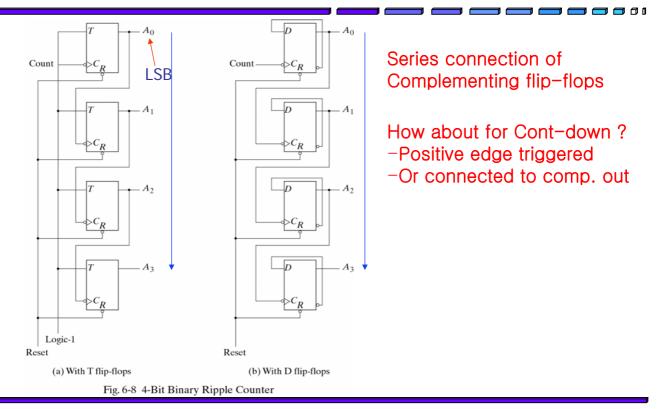

#### Counters

- A register that goes through a prescribed sequence of states upon the application of input pulses is called a counter.

- The input pulses may be clock pulses or they may originated from some external source and may occur at a fixed interval of time or at random.

- A counter that follows the binary number sequence is called a binary counter.

- An n-bit binary counter consists of n flip-flops and can count in binary from 0 through 2<sup>n</sup> -1.

Korea University of Technology and Education

#### Counters

- Counters in two categories

- Ripple counters

- Synchronous counters

#### Ripple counters

- The flip-flop output transition serves as a source for triggering other flip-flops.

- The C input some or all flip-flops are triggered not by the common clock pulses, but rather by the transition that occurs in other flip-flop outputs.

#### Synchronous counters

• The C inputs of all flip-flops receive the common clock .

#### **Binary Ripple Counters**

Korea University of Technology and Education

#### Count Sequence for a Binary Ripple Counter

**d** 0 1

| Count sequence<br>A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> |                                                                                                                                      | Conditions for<br>Complementing                                                                                                                                                           |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                          | Complement Ao<br>Complement Ao<br>Complement Ao<br>Complement Ao<br>Complement Ao<br>Complement Ao<br>Complement Ao<br>Complement Ao | A₀ will go from 1 to 0 and<br>complement A₁<br>A₀ will go from 1 to 0 and<br>complement A₁ ;<br>A₁will go from 1 to 0 and<br>complement A₂<br>A₀ will go from 1 to 0 and<br>complement A₁ |

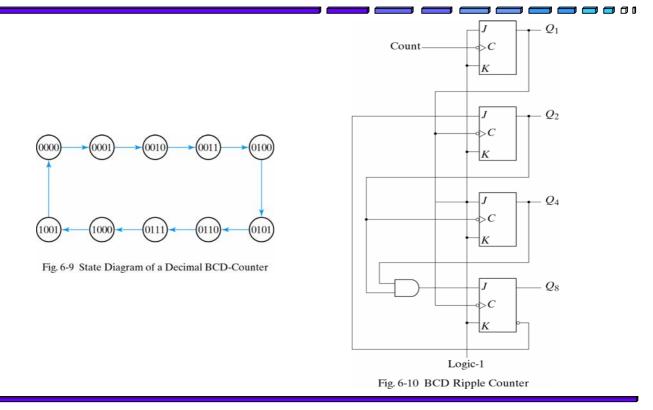

#### BCD Ripple Counter

Korea University of Technology and Education

#### BCD Ripple Counter

- Q1 is complemented on the negative edge of every count pulse.

- Q2 is complemented if Q8=0 and Q1 goes from 1 to 0. Q2 is cleared if Q8=1 and Q1 goes from 1 to 0.

- Q4 is complemented when Q2 goes from 1 to 0.

- Q8 is complemented when Q4Q2=11 and Q1 goes from 1 to 0. Q8 is cleared if either Q4 or Q2 is 0 and Q1 goes from 1 to 0

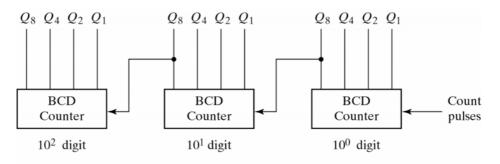

#### Three-Decade Decimal BCD Counter

101

Fig. 6-11 Block Diagram of a Three-Decade Decimal BCD Counter

- □ To count from 0 to 999, We need a three-decade counter.

- □ When Q8 in one decade goes from 1 to 0, it triggers the count

Korea University of Technology and Education

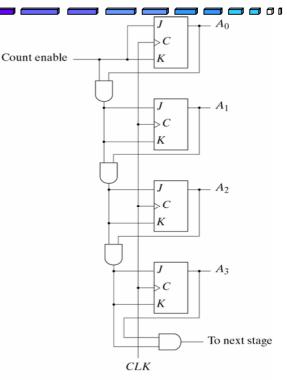

#### Synchronous Counters

- Clock pulses are applied to the inputs of all flip-flops

- A common clock triggers all flip-flops simultaneously rather than one at a time as in a ripple counter

#### Synchronous Binary Counter

- The first stage A0 has its J and K equal to 1 if the counter is enabled.

- The other J and K inputs are equal to 1 if all previous loworder bits are equal to 1 and the count is enabled.

- A flip-flop in any other position is complemented when all the bits in the lower significant positions are equal to 1

- A3A2A1A0=0011 -> 0100

Fig. 6-12 4-Bit Synchronous Binary Counter

Korea University of Technology and Education

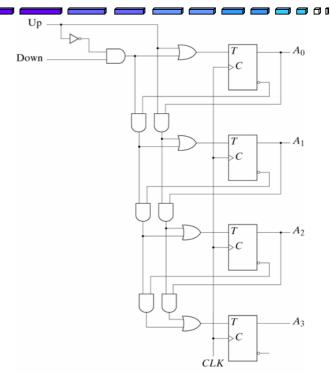

#### Up-Down Binary Counter

- Up input control=1 ;count up (the T inputs receive their signals from the values of the previous normal outputs of the flipflops.)

- Down input control=1, up input control=0 ; count down

- Up=down=0 ;unchanged state

- Up=down=1 ;count up

Fig. 6-13 4-Bit Up-Down Binary Counter

# BCD Counter

| Present State  |    |    |    | Next State         |       |           |          | Output   | Flip-Flop Inputs |     |     |    |  |

|----------------|----|----|----|--------------------|-------|-----------|----------|----------|------------------|-----|-----|----|--|

| Q <sub>8</sub> | Q4 | Q2 | Q1 | Q <sub>8</sub>     | Q4    | Q2        | Q1       | y        | TQ <sub>8</sub>  | TQ4 | TQ2 | TQ |  |

| 0              | 0  | 0  | 0  | 0                  | 0     | 0         | 1        | 0        | 0                | 0   | 0   | 1  |  |

| 0              | 0  | 0  | 1  | 0                  | 0     | 1         | 0        | 0        | 0                | 0   | 1   | 1  |  |

| 0              | 0  | 1  | 0  | 0                  | 0     | 1         | 1        | 0        | 0                | 0   | 0   | 1  |  |

| 0              | 0  | 1  | 1  | 0                  | 1     | 0         | 0        | 0        | 0                | 1   | 1   | 1  |  |

| 0              | 1  | 0  | 0  | 0                  | 1     | 0         | 1        | 0        | 0                | 0   | 0   | 1  |  |

| 0              | 1  | 0  | 1  | 0                  | 1     | 1         | 0        | 0        | 0                | 0   | 1   | 1  |  |

| 0              | 1  | 1  | 0  | 0                  | 1     | 1         | 1        | 0        | 0                | 0   | 0   | 1  |  |

| 0              | 1  | 1  | 1  | 1                  | 0     | 0         | 0        | 0        | 1                | 1   | 1   | 1  |  |

| 1              | 0  | 0  | 0  | 1                  | 0     | 0         | 1        | 0        | 0                | 0   | 0   | 1  |  |

| 1              | 0  | 0  | 1  | 0                  | 0     | 0         | 0        | 1        | 1                | 0   | 0   | 1  |  |

|                |    |    |    | ΤQ                 | 1=1   |           |          |          |                  |     |     |    |  |

|                |    |    |    | T q                | 2 = Q | $2'^8Q_1$ | l        |          |                  |     |     |    |  |

|                |    |    |    | $T_{Q4} = Q_2 Q_1$ |       |           |          |          |                  |     |     |    |  |

|                |    |    |    |                    |       |           | $+0_{4}$ | $Q_2Q_1$ |                  |     |     |    |  |

|                |    |    |    | -                  | = Q8Q | ~         | ' £''    | e-z'     |                  |     |     |    |  |

Korea University of Technology and Education

#### Example

Design a synchronous BCD counter with J-K flip-flops.

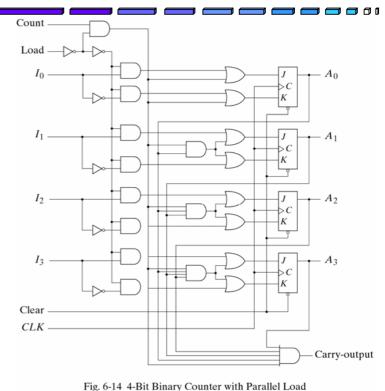

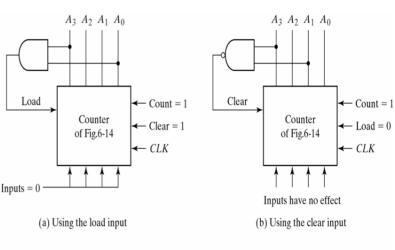

#### Binary Counter with Parallel Load

- Parallel load for initial number

- Input load control=1; disables the count sequence, data transfer

- Load =0 and count=1 ;count

- Load=0 and count=0 ;unchanged

- Carry out=1 (all flipflop=1 and Count=1)

Korea University of Technology and Education

# BCD Counter using Binary Counter with Parallel

- The AND gate detects the occurrence of state 1001(9) in the output. In this state, the load input is enabled and all-0's input is loaded into register.

- The NAND gate detects the count of 1010(10), as soon as this count occurs the register is cleared.

- A momentary spike occurs in output A2 as the count goes from 1001 to 1010 and immediately to 0000

Fig. 6-15 Two ways to Achieve a BCD Counter Using a Counter with Parallel Load

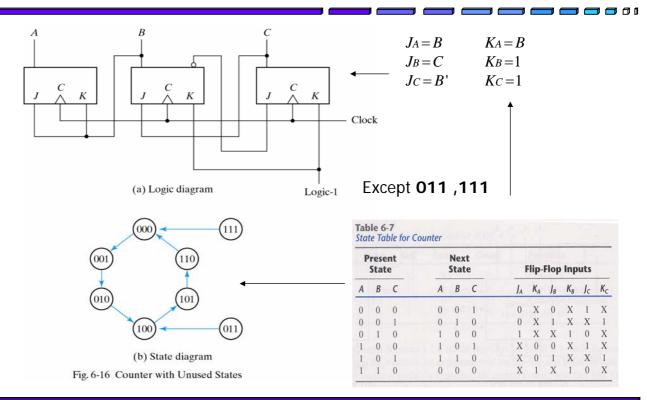

# Other Counters

Korea University of Technology and Education

#### Example

• Design a counter with the following repeated binary sequence: 0, 1, 2, 4, 6. Use D flip-flops

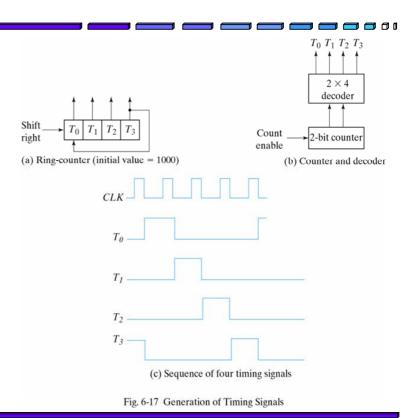

## Ring Counter

- For generating timing signal that control the sequence of operations

- A circular shift register with only one flip-flop being set at any particular time; all others are cleared.

- The single bit is shifted from one flip-flop to the other.

- 2<sup>n</sup> timing signals need

2<sup>n</sup> flip-flops

Korea University of Technology and Education

#### Johnson Counter

- A circular shift register with the complement output of the last flipflop connected to the input of the first flipflop.

- A k-bit switch-tail ring counter will go through a sequence of 2k states.

- A Johnson counter is a k-bit switch-tail ring counter with 2k decoding gates to provide outputs for 2k timing signals.

(a) Four-stage switch-tail ring counter

| Sequence | Fli | p-flop | outpu | AND gate require |            |  |  |

|----------|-----|--------|-------|------------------|------------|--|--|

| number   | A   | В      | С     | E                | for output |  |  |

| 1        | 0   | 0      | 0     | 0                | A'E'       |  |  |

| 2        | 1   | 0      | 0     | 0                | AB'        |  |  |

| 3        | 1   | 1      | 0     | 0                | BC'        |  |  |

| 4        | 1   | 1      | 1     | 0                | CE'        |  |  |

| 5        | 1   | 1      | 1     | 1                | AE         |  |  |

| 6        | 0   | 1      | 1     | 1                | A'B        |  |  |

| 7        | 0   | 0      | 1     | 1                | B'C        |  |  |

| 8        | 0   | 0      | 0     | 1                | C'E        |  |  |

(b) Count sequence and required decoding

Fig. 6-18 Construction of a Johnson Counter

#### Memory Decoding

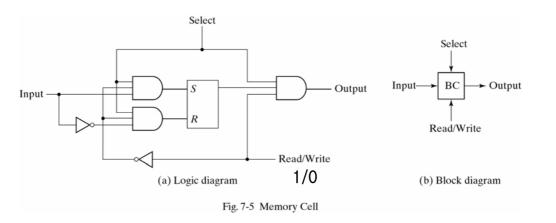

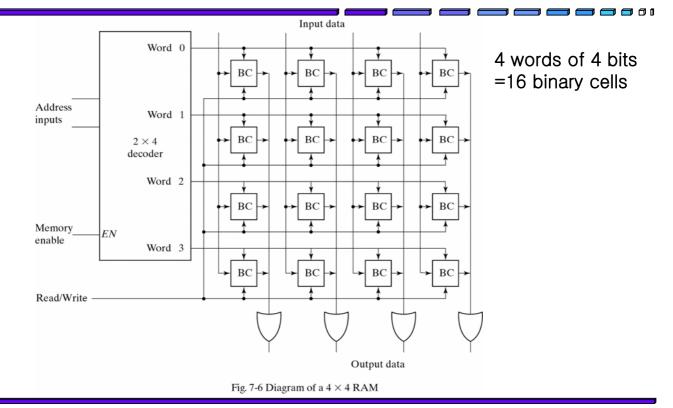

The equivalent logic of a binary cell that stores one bit of information 7 0 1

- The binary cell stores one bit in its internal flip-flop

- It has three inputs and one output. The read/write input determines the cell operation when it is selected.

Korea University of Technology and Education

#### Internal Construction

Korea University of Technology and Education

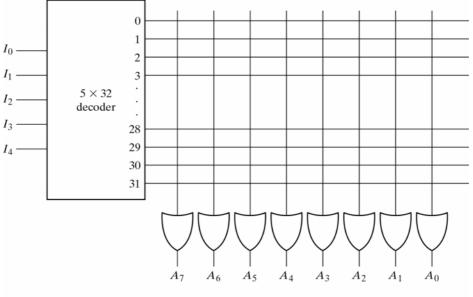

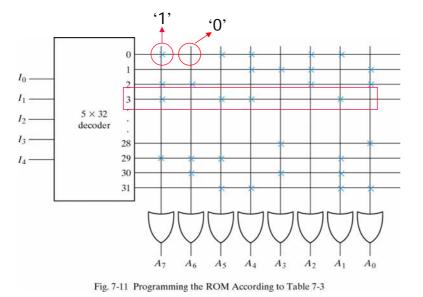

#### Read-Only Memory

ROM = AND gates connected as a decoder + a number of OR gates

**d d d d**

1 🗖 🖉 1

Fig. 7-10 Internal Logic of a  $32 \times 8$  ROM

Korea University of Technology and Education

#### ROM Truth Table (Partial)

| Table 7-3        |                 |

|------------------|-----------------|

| <b>ROM Truth</b> | Table (Partial) |

| Inputs |    |    |    | Outputs |        |    |    |    |    |    |    |    |

|--------|----|----|----|---------|--------|----|----|----|----|----|----|----|

| 14     | 13 | 12 | 11 | 10      | <br>A7 | A6 | A5 | A4 | A3 | A2 | A1 | AO |

| 0      | 0  | 0  | 0  | 0       | 1      | 0  | 1  | 1  | 0  | 1  | 1  | 0  |

| 0      | 0  | 0  | 0  | 1       | 0      | 0  | 0  | 1  | 1  | 1  | 0  | 1  |

| 0      | 0  | 0  | 1  | 0       | 1      | 1  | 0  | 0  | 0  | 1  | 0  | 1  |

| 0      | 0  | 0  | 1  | 1       | 1      | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

|        |    | :  |    |         |        |    | 3  |    |    |    |    |    |

| 1      | 1  | 1  | 0  | 0       | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 1  |

| 1      | 1  | 1  | 0  | 1       | 1      | 1  | 1  | 0  | 0  | 0  | 1  | 0  |

| 1      | 1  | 1  | 1  | 0       | 0      | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| 1      | 1  | 1  | 1  | 1       | 0      | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

#### Combinational Circuit Implementation

A<sub>7</sub>(I<sub>4</sub>,I<sub>3</sub>,I<sub>2</sub>,I<sub>0</sub>)=Sum of minterms(0,2,3,...,29)

**d d d d**

Input->00011(3) Others-> all '0' Output->10110010

Korea University of Technology and Education

Korea University of Technology and Education