# ATmega128 Interrupt

#### Jee-Hwan Ryu

School of Mechanical Engineering

Korea University of Technology and Education

# 인터럽트(Interrupt, 가로채기)의 개념

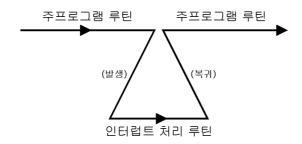

- CPU외부의 하드웨어적인 요구에 의해서 정상적인 프로그램의 실행 순서를 변경하여 보다 시급한 작업을 먼저 수행한 후에 다시 원래의 프로그램으로 복귀하는 것

- 비동기적으로 발생하는 주변장치의 서비스 요청에 CPU가 가장 빠르게 대응 할 수 있는 방법

- 비동기적으로 동작하는 CPU(고속)와 주변장치(저속) 사이에서 효율적으로 일을 수행

- 인터럽트가 발생하면 나중에 돌아올 복귀주소(return address)가 자동적으로 스택에 저장되었다가, 인터럽트 서비스루틴의 마지막에서 복귀 명령을 만나면 다시 자동적으로 복귀주소로 돌아온다.

## 인터럽트의 종류

- 인터럽트 발생원인에 따른 분류

- 하드웨어 인터럽트

- 내부 인터럽트

- 외부 인터럽트

- 소프트웨어 인터럽트

- 인터럽트 발생시 마이크로프로세서의 반응 방식에 따른 분류

- 차단 가능 인터럽트

- 차단 불가능 인터럽트

- 인터럽트를 요구한 입출력 기기를 확인하는 방법에 따른 분류

- 벡터형 인터럽트 (vectored interrupt)

- 조사형 인터럽트 (polled interrupt)

#### Korea University of Technology and Education

### 내부 인터럽트

- CPU에 정의되어 있지 않은 명령의 실행

- Zero로 나눗셈을 시도

- 보호된 메모리 영역에 접근 등의 원인에 의해 마이크로프 로세서 내부적으로 발생되는 인터럽트

- ATmega128은 내부 인터럽트가 없다.

## 외부 인터럽트

- 타이머에서 지정된 시간 경과

- 입력장치에서의 서비스 요구

- 출력장치의 작업종료

- A/D 변환의 완료

- DMA 동작의 종료

- 멀티프로세서간의 통신 요구 등 마이크로프로세서와 독립되어 있는 외부장치에 의해 발생되는 순수한 의미에서의 인터럽트

#### Korea University of Technology and Education

## 차단 가능/불가능 인터럽트

- 차단 가능 인터럽트

- 프로그래머에 의하여 인터럽트 요청을 받아들이지 않고 무시할 수 있는 것

- 시간제약이 중요한 프로그램 수행 중에는 인터럽트 요청을 허용 하지 않을 수 있다.

- 차단 불가능 인터럽트

- 프로그래머에 의하여 어떤 방법으로도 인터럽트 요청이 차단될 수 없는 것

- 전원이상, 비상정지 스위치 등 돌발사태에 대비하기 위한 것

## 인터럽트 차단 및 허용

- 인터럽트 마스크 레지스터, 인터럽트 허용 레지스터를 사용하여 개별적으로 차단 및 허용 가능

- EIMSK: 개별적 인터럽트의 차단/허용

- SEI: Set Global Interrupt Flag, Global Interrupt Enable

- CLI: Clear Global Interrupt Flag, Global Interrupt Disable

#### Korea University of Technology and Education

## 벡터형 인터럽트

- 인터럽트가 발생할 때마다 인터럽트를 요청한 장치가 인 터럽트 서비스 루틴의 시작번지를 CPU에게 전송하거나, 또는 CPU가 각 인터럽트의 종류에 따라 미리 지정된 메 모리 번지에서 인터럽트 벡터를 읽어서 이를 인터럽트 서 비스 루틴의 시작번지로 사용하는 방식

- 인터럽트 시간이 빠르다

- 주변장치의 많고 적음에 영향이 없다.

- ATmega128의 모든 인터럽트는 이 방식

## 조사(polling)형 인터럽트

- 인터럽트가 발생하면 이 인터럽트를 요청한 장치를 찾기 위하여 CPU가 각 주변장치를 소프트웨어적으로 차례로 조사(polling)하는 방식

- 하드웨어 간단

- 주변장치의 많고 적음에 따라 처리시간이 변함

- ATmega128은 사용하지 않는다.

#### Korea University of Technology and Education

## 인터럽트의 우선순위 제어

- 인터럽트 우선순위 제어가 필요한 경우

- 우연히 2개 이상의 주변장치가 동시에 CPU에게 인터럽트를 요청하는 경우

- 하나의 인터럽트가 서비스되고 있는 동안에 또 다른 인터럽트가 요청되는 경우

- 벡터형 인터럽트의 경우

- 인터럽트 우선순위 제어기의 우선순위 레지스터의 초기화로 우선 순위 제어방식 사용

- 조사형 인터럽트의 경우

- 폴링의 순서에 의하여 소프트웨어적으로 우선순위 선정

# ATmega128의 인터럽트

### • 34종의 차단가능 외부 인터럽트

Table 23. Reset and Interrupt Vectors

| Vector<br>No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                                 |

|---------------|-----------------------------------|--------------|--------------------------------------------------------------------------------------|

| 1             | \$0000(1)                         | RESET        | External Pin, Power-on Reset, Brown-out Reset,<br>Watchdog Reset, and JTAG AVR Reset |

| 2             | \$0002                            | INT0         | External Interrupt Request 0                                                         |

| 3             | \$0004                            | INT1         | External Interrupt Request 1                                                         |

| 4             | \$0006                            | INT2         | External Interrupt Request 2                                                         |

| 5             | \$0008                            | INT3         | External Interrupt Request 3                                                         |

| 6             | \$000A                            | INT4         | External Interrupt Request 4                                                         |

| 7             | \$000C                            | INT5         | External Interrupt Request 5                                                         |

| 8             | \$000E                            | INT6         | External Interrupt Request 6                                                         |

| 9             | \$0010                            | INT7         | External Interrupt Request 7                                                         |

| 10            | \$0012                            | TIMER2 COMP  | Timer/Counter2 Compare Match                                                         |

| 11            | \$0014                            | TIMER2 OVF   | Timer/Counter2 Overflow                                                              |

| 12            | \$0016                            | TIMER1 CAPT  | Timer/Counter1 Capture Event                                                         |

| 13            | \$0018                            | TIMER1 COMPA | Timer/Counter1 Compare Match A                                                       |

| 14            | \$001A                            | TIMER1 COMPB | Timer/Counter1 Compare Match B                                                       |

| 15            | \$001C                            | TIMER1 OVF   | Timer/Counter1 Overflow                                                              |

#### Korea University of Technology and Education

# ATmega128의 인터럽트

|    |                       | 1            |                                |

|----|-----------------------|--------------|--------------------------------|

| 16 | \$001E                | TIMER0 COMP  | Timer/Counter0 Compare Match   |

| 17 | \$0020                | TIMER0 OVF   | Timer/Counter0 Overflow        |

| 18 | \$0022                | SPI, STC     | SPI Serial Transfer Complete   |

| 19 | \$0024                | USART0, RX   | USART0, Rx Complete            |

| 20 | \$0026                | USART0, UDRE | USART0 Data Register Empty     |

| 21 | \$0028                | USART0, TX   | USART0, Tx Complete            |

| 22 | \$002A                | ADC          | ADC Conversion Complete        |

| 23 | \$002C                | EE READY     | EEPROM Ready                   |

| 24 | \$002E                | ANALOG COMP  | Analog Comparator              |

| 25 | \$0030 <sup>(3)</sup> | TIMER1 COMPC | Timer/Countre1 Compare Match C |

| 26 | \$0032 <sup>(3)</sup> | TIMER3 CAPT  | Timer/Counter3 Capture Event   |

| 27 | \$0034 <sup>(3)</sup> | TIMER3 COMPA | Timer/Counter3 Compare Match A |

| 28 | \$0036 <sup>(3)</sup> | TIMER3 COMPB | Timer/Counter3 Compare Match B |

| 29 | \$0038 <sup>(3)</sup> | TIMER3 COMPC | Timer/Counter3 Compare Match C |

| 30 | \$003A <sup>(3)</sup> | TIMER3 OVF   | Timer/Counter3 Overflow        |

#### 인터럽트의 동작

- 어느 인터럽트가 요청되어 이것이 허용되면 인터럽트 서비스 루틴이 실행되면서 SREG 레지스터의 글로벌 인터럽트 허용비트 I가 0으로 클리어되어 모든 인터럽트가 금지상태로 된다.

- 인터럽트 서비스 루틴이 실행되는 동안에 다른 인터럽트 가 발생되도록 다중인터럽트를 허용하려면 SREG레지스 터의 I비트를 1로 설정해야 한다.

- ISR을 종료하기 위하여 복귀명령을 실행하면 I가 다시 1 로 되살아나 인터럽트 허용상태로 복귀된다.

#### Korea University of Technology and Education

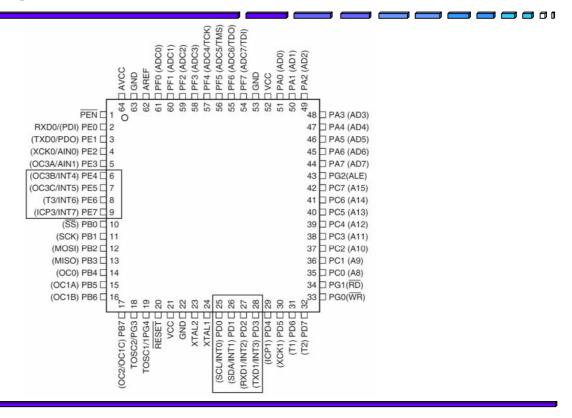

## ATmega128의 외부 인터럽트

- 8개의 외부핀 INT7~0을 통해 입력되는 신호에 의하여 발생되는 인터럽트

- 이 핀들을 출력으로 설정하여도 발생 -> 병렬 I/O포트에 소프트웨어적으로 데이터를 출력하여 인터럽트 요구가능

- 트리거 방법

- EICRA(INT3~0), EICRB(INT7~4) 사용하여 설정

- Low level, falling edge, rising edge 에 의하여 트리거

# ATmega128의 외부 인터럽트 핀

Korea University of Technology and Education

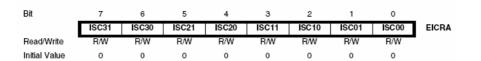

## EICRA (External Interrupt Control Register A)

| ISCn1 | ISCn0 | Description                                                             |

|-------|-------|-------------------------------------------------------------------------|

| 0     | 0     | The low level of INTn generates an interrupt request.                   |

| 0     | 1     | Reserved                                                                |

| 1     | 0     | The falling edge of INTn generates asynchronously an interrupt request. |

| 1     | 1     | The rising edge of INTn generates asynchronously an interrupt request.  |

Korea University of Technology and Education

## EICRB (External Interrupt Control Register B)

| ISCn1 | ISCn0 | Description                                                                  |

|-------|-------|------------------------------------------------------------------------------|

| 0     | 0     | The low level of INTn generates an interrupt request.                        |

| 0     | 1     | Any logical change on INTn generates an interrupt request                    |

| 1     | 0     | The falling edge between two samples of INTn generates an interrupt request. |

| 1     | 1     | The rising edge between two samples of INTn generates an interrupt request.  |

Note: 1. n = 7, 6, 5 or 4.

#### Korea University of Technology and Education

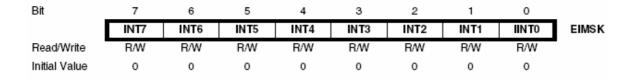

## EIMSK (External Interrupt Mask Register)

- INT7~0를 개별적으로 허용하는데 사용

- 1:허용, 0:금지

- 개별적으로 허용된 인터럽트는 다시 SREG의 I(글로벌 인 터럽트 허용 비트)가 1로 설정되어야 실제로 허용

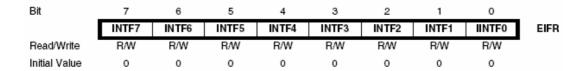

# EIFR (External Interrupt Flag Register)

- INT7~0핀에 인터럽트 신호가 입력되어 해당인터럽트가 트리거 되었음 표시

- 인터럽트 서비스루틴으로 점프하면 다시 0으로 클리어됨

Korea University of Technology and Education